Table of Contents

The following lists show important hardware details of all supported hardware platforms of this VisualApplets version. For a detailed list, please check the data sheet of the individual product.

| Resource | imaFlex CXP-12 Quad | imaFlex CXP-12 Penta |

|---|---|---|

| Vision Processor | Xilinx UltraScale+ XCKU3P-FFVD900-1-E | Xilinx UltraScale+ XCKU3P-FFVB676-1-E |

| LUT | 160679 | 161049 |

| Flip-Flop | 323224 | 323216 |

| Block RAM (18k) | 720 | 720 |

| URAM Blocks (288k) | 48 | 48 |

| Embedded Arithmetic Logic Unit (DSP48) | 1368 | 1368 |

| RAM size | 3 x 512 MiB DDR4 | 5 x 512 MiB DDR4 |

| RAM Data Width | 384 Bit | 640 Bit |

| RAM Bandwidth total (shared) | 14.4 GB/s* | 24.0 GB/s* |

| Base Design Clock (default) | 312.5 MHz** | 312.5 MHz** |

| Base Design Clock (maximal) | 400.0 MHz | 400.0 MHz |

| Host Interface | PCIe x 8 Gen 3 (Direct Memory Access) | PCIe x 8 Gen 3 (Direct Memory Access) |

| Host Interface (PCIe x 8 Gen 3) Bandwidth (theor.) | 8000 MB/s | 8000 MB/s |

| Host Interface (PCIe x 8 Gen 3) Bandwidth (typ./max.) | 7200 MB/s sustainable data bandwidth | 7200 MB/s sustainable data bandwidth |

|

* The platform includes a single physical RAM bank. Although each RAM-based operator uses a dedicated memory segment, the overall RAM size and memory bandwidth are shared across all operators. See also section ' Shared Memory Concept '. ** This platform allows to use a user-specified base clock. The minimum supported clock frequency is 312.5 MHz while the theoretical maximum is 400 MHz. Designs running at 312.5 MHz are generally expected to meet timing constraints. Frequencies above 312.5 MHz may lead to timing violations, depending on the implementation of the applet algorithms. |

||

Table 66. Hardware Configuration imaFlex CXP-12 Quad and imaFlex CXP-12 Penta

| Resource | mE5 marathon VCX-QP | mE5 marathon VF2 | mE5 marathon VCL | mE5 marathon VCLx | LightBridge 2 VCL |

|---|---|---|---|---|---|

| Vision Processor | Xilinx Kintex7 XC7K160T - 2FFG676C FPGA | Xilinx Kintex7 XC7K160T - 2FFG676C FPGA | Xilinx Kintex7 XC7K160T - 1FBG676C FPGA | Xilinx Kintex7 XC7K410T - 1FBG676C FPGA | Xilinx Kintex7 XC7K160T - 1FBG676C FPGA |

| LUT | 101400 | 101400 | 101400 | 254200 | 101400 |

| Flip-Flop | 202800 | 202800 | 202800 | 508400 | 202800 |

| Block RAM (18k) | 650 | 650 | 650 | 1590 | 650 |

| Embedded Arithmetic Logic Unit (DSP48) | 600 | 600 | 600 | 1540 | 600 |

| RAM size | 4 x 512MiB DDR3 | 4 x 512MiB DDR3 | 4 x 512MiB DDR3 | 4 x 512MiB DDR3 | 4 x 512MiB DDR3 |

| RAM Data Width | 512 Bit | 512 Bit | 256 Bit | 256 Bit | 256 Bit |

| RAM Bandwidth total (shared) | 12.8 GB/s* | 12.8 GB/s* | 6.4 GB/s* | 6.4 GB/s* | 6.4 GB/s* |

| Base Design Clock (default) | 125MHz | 125MHz | 125MHz | 125MHz | 125MHz |

| Base Design Clock (maximal) | 312.5 MHz** | 312.5 MHz** | 312.5 MHz** | 312.5 MHz** | 312.5 MHz** |

| Host Interface | PCIe x 4 Gen 2 (Direct Memory Access) | PCIe x 4 Gen 2 (Direct Memory Access) | PCIe x 4 Gen 2 (Direct Memory Access) | PCIe x 4 Gen 2 (Direct Memory Access) | PCIe x 4 Gen 2 interface via Thunderbolt™ 2 technology |

| Host Interface (PCIe x 4 Gen 2) Bandwidth (theor.) | 1x2000 MB/s | 1x2000 MB/s | 1x2000 MB/s | 1x2000 MB/s | 1x2000 MB/s |

| Host Interface (PCIe x 4 Gen 2) Bandwidth (typ./max.) | Up 1800 MB/s sustainable data bandwidth | Up to 1800 MB/s sustainable data bandwidth | Up to 1800 MB/s sustainable data bandwidth | Up to 1800 MB/s sustainable data bandwidth | Up to 1400 MB/s sustainable data bandwidth |

|

* The platforms own only one single physical RAM bank which is formatted as 4 independent, non-overlapping memory regions. Though the memory itself is exclusive for each RAM based operator, the RAM bandwidth is shared. See section Shared Memory Concept. ** These platforms allow to use a user-specified base clock. The minimum clock frequency is 125 MHz. Theoretical maximum is 312.5 MHz. Designs with a clock frequency of 125 MHz are likely to meet the timing constraints. Designs with a clock frequency above 125 MHz may result in timing constraints violations. |

|||||

Table 67. Hardware Configuration LightBridge and microEnable 5 marathon

| Resource | mE5VD8-PoCL | mE5VQ8-CXP6B/mE5VQ8-CXP6D |

|---|---|---|

| Vision Processor | Xilinx Virtex6 XC6VLX240T FPGA | Xilinx Virtex6 XC6VLX240T FPGA |

| LUT | 150720 | 150720 |

| Flip-Flop | 301440 | 301440 |

| Block RAM | 832 x 18432Bit | 832 x 18432Bit |

| Embedded Arithmetic Logic Unit (DSP48) | 768 | 768 |

| RAM | 4 x 256MiB DDR3 | 4 x 256MiB DDR3 |

| Data Width per RAM | 128Bit | 128Bit |

| Bandwidth per RAM | 4GB/s | 4GB/s |

| Base Design Clock | 125MHz | 125MHz |

| Host Interface | PCIe x8 Gen2 | PCIe x8 Gen2 |

| Host Interface (PCIe x 8 Gen 2) Bandwidth (theor.) | 4 Gbyte/s per direction on PCIe bus | 4 Gbyte/s per direction on PCIe bus |

| Host Interface (PCIe x 8 Gen 2) Bandwidth (typ./max.) | up to 3.6 GByte/s on PCIe bus | up to 3.6 GByte/s on PCIe bus |

Table 68. Hardware Configuration microEnable 5 ironman

Device resources are limited on each hardware platform. The lists below show the available resources for all supported platforms. Operators consume device resources, and each resource instance can be used only once.

Device resources are allocated either

-

automatically,

-

using operator parameters, or

-

in the Resources dialog.

See 'Allocation of Device Resources' for more information.

| Resource | imaFlex CXP-12 Quad | imaFlex CXP-12 Penta |

|---|---|---|

| Camera Port | 4 | 5 |

| CxpStatusPort | 4 | 5 |

| CxpRxTriggerPort | 4 | 5 |

| CxpTxTriggerPort | 4 | 5 |

| DMA | 4 | 5 |

| DmaFromHostPort | 1 | 1 |

| GPO* | 10 OUT | 12 OUT |

| GPI** | 12 IN | 12 IN |

| LED Ports* | 6 | 6 |

| SignalChannel*** | 4000 | 4000 |

| EventPort**** | 32 | 32 |

| EventID**** | 64 | 64 |

| ImageChannel***** | 1024 | 1024 |

| RAM****** | from 1 x 1.5 GiB to 8 x 192 MiB | from 1 x 2.5 GiB to 8 x 320 MiB |

|

* These resources are not visible in the Resources dialog. They are controlled via operators. ** GPI is not visible in the Resources dialog. The same resource can be used multiple times. The table lists the amount of GPI ports. *** Resource SignalChannel allows to connect TxSignalLink operators with RxSignalLink operators. Each operator TxSignalLink needs one resource SignalChannel exclusively. Multiple operators RxSignalLink can use the same resource SignalChannel, i.e., multiple operators RxSignalLink can receive the signals transmitted by one operator TxSignalLink. A maximum of 4000 TxSignalLink operators can be used in a design. The number of RxSignalLink operators is not restricted. Resource SignalChannel is visible in the Resources dialog. **** “EventID” refers to the maximum number of events supported by the software for the given platform. “EventPort” represents the event channel. Each channel can handle up to 16 events. ***** Resource ImageChannel allows to connect TxImageLink operators with RxImageLink operators. Each operator TxImageLink needs one resource ImageChannel exclusively. Each resource ImageChannel can be connected to exactly one operator RxImageLink, i.e., a maximum of 1024 TxImageLink and 1024 RxImageLink operators can be used in one design. Resource ImageChannel is visible in the Resources dialog. ****** RAM interface is shared across all RAM based operators in bandwidth and size. See section Shared Memory Concept for more details. |

||

Table 69. List of Device Resources imaFlex CXP-12 Quad and imaFlex CXP-12 Penta

| Resource | mE5 marathon VCX-QP | mE5 marathon VF2 | mE5 marathon VCL | mE5 marathon VCLx | LightBridge VCL |

|---|---|---|---|---|---|

| Camera Port | 4 | 2 | 2 | 2 | 2 |

| CameraControl | - | - | 2 | 2 | 2 |

| DMA | 4 | 4 | 4 | 4 | 4 |

| GPO* | 10 OUT | 10 OUT | 10 OUT | 10 OUT | 6 OUT |

| GPI** | 12 IN | 12 IN | 12 IN | 12 IN | 8 IN |

| RAM | 4 x 512 MiB | 4 x 512 MiB | 4 x 512 MiB | 4 x 512 MiB | 4 x 512 MiB |

| LED Ports* | 4 | 4 | 2 | 2 | 2 |

| SignalChannel*** | 4000 | 4000 | 4000 | 4000 | 4000 |

| EventPort**** | 14 | 14 | 10 | 10 | 10 |

| EventID**** | 64 | 64 | 64 | 64 | 64 |

| ImageChannel***** | 1024 | 1024 | 1024 | 1024 | 1024 |

|

* These resources are not visible in the Resources dialog. They are controlled via operators. ** GPI is not visible in the Resources dialog. The same resource can be used multiple times. The table lists the amount of GPI ports. *** Resource SignalChannel allows to connect TxSignalLink operators with RxSignalLink operators. Each operator TxSignalLink needs one resource SignalChannel exclusively. Multiple operators RxSignalLink can use the same resource SignalChannel, i.e., multiple operators RxSignalLink can receive the signals transmitted by one operator TxSignalLink. A maximum of 4000 TxSignalLink operators can be used in a design. The number of RxSignalLink operators is not restricted. Resource SignalChannel is visible in the Resources dialog. **** "EventID" stands for maximal amount of events supported by the software for the particular platform. "EventPort" represents the event channel. One event channel can host up to 16 events. ***** Resource ImageChannel allows to connect TxImageLink operators with RxImageLink operators. Each operator TxImageLink needs one resource ImageChannel exclusively. Each resource ImageChannel can be connected to exactly one operator RxImageLink, i.e., a maximum of 1024 TxImageLink and 1024 RxImageLink operators can be used in one design. Resource ImageChannel is visible in the Resources dialog. |

|||||

Table 70. List of Device Resources LightBridge and microEnable 5 marathon

| Resource | mE5VD8-PoCL | mE5VQ8-CXP6D/mE5VQ8-CXP6B |

|---|---|---|

| Camera Port | 2 | 4 |

| DMARd | 4 | 4 |

| GPO* | 8 OUT | 8 OUT |

| RAM | 4 x 256MiB | 4 x 256MiB |

| LED Ports* | 4 | 4 |

| GPI** | 8 | 8 |

| SignalChannel*** | 4000 | 4000 |

| EventPort**** | 12 | 14 |

| EventID**** | 64 | 64 |

| ImageChannel***** | 1024 | 1024 |

|

* These resources are not visible in the Resources dialog. They are controlled via operators. ** GPI is not visible in the Resources dialog. The same resource can be used multiple times. The table lists the amount of GPI ports. *** Resource SignalChannel allows to connect TxSignalLink operators with RxSignalLink operators. Each operator TxSignalLink needs one resource SignalChannel exclusively. Multiple operators RxSignalLink can use the same resource SignalChannel, i.e., multiple operators RxSignalLink can receive the signals transmitted by one operator TxSignalLink. A maximum of 4000 TxSignalLink operators can be used in a design. The number of RxSignalLink operators is not restricted. Resource SignalChannel is visible in the Resources dialog. **** EventID stands for maximal amount of events supported by the software for the particular platform. EventPort represents the event channel. One event channel can host up to 16 events. ***** Resource ImageChannel allows to connect TxImageLink operators with RxImageLink operators. Each operator TxImageLink needs one resource ImageChannel exclusively. Each resource ImageChannel can be connected to exactly one operator RxImageLink, i.e., a maximum of 1024 TxImageLink and 1024 RxImageLink operators can be used in one design. Resource ImageChannel is visible in the Resources dialog. |

||

Table 71. List of Device Resources microEnable 5 ironman

The platforms imaFlex CXP-12 Quad and imaFlex CXP-12 Penta are assembled with only one physical RAM bank (the size of which is platform-specific). This single physical bank is dynamically formatted into non-overlapping regions depending on the amount of used RAM-based VisualApplets operators inside the applet. Those regions are represented inside VisualApplets as virtual RAM banks. When an operator reserves a RAM resource, it is using a virtual RAM bank which maps to an exclusive non-overlapping memory region inside the physical RAM. Up to 8 non-overlapping regions can be defined on the imaFlex platforms. When only 1 RAM operator is used, the operator gets the complete RAM size of the platform. The allocated size for each operator is reduced for each operator used in the design. If 8 operators are used, each operator will allocated 1/8 of the platform memory size.

The RAM bandwidth, however, is shared between all RAM-based operators in a design. When a design utilizes all 8 RAM resources, each of the 8 RAM-based operators can have up to 1/8 GB/s exclusive bandwidth, minus the efficiency factor of that particular operator. When only one RAM-based operator is used in the design, this operator gets the total bandwidth of the platform. When 2 operators are used, each of the two operators gets half the total bandwidth, etc.

Not allocated and thus not used RAM ports get always 0% of the memory size.

-

1 port is utilized: the utilized port gets 100%.

-

2 ports are utilized: both utilized ports get 50%.

-

3 ports are utilized: the port with the lowest resource ID number will get 50%, the other 2 utilized ports get 25%.

-

4 ports are utilized: all 4 ports get 25%.

-

5 ports are utilized: 3 ports with the lowest resource ID number will get 25%. The last 2 ports will get 12.5%.

-

6 ports are utilized: 2 ports with the lowest resource ID number will get 25%. The other 4 ports will get 12.5%.

-

7 ports are utilized: the port with the lowest resource ID number will get 25%. The other 6 ports will get 12.5%.

-

8 ports are utilized: all ports get 12.5%.

![[Note]](../common/images/admon/note.png) |

|

|

Ports with the lower RAM index will get larger allocation in case of asymmetric size partitioning. For example 3 RAM ports are used: 0, 1, 2. The port 0 gets 50% RAM size allocation. The ports 1 and 2 get both 25% each. The RAM indexes do not need to be contiguous, their absolute order decides the allocation. The RAM index is a virtual number and has no impact on FPGA resource usage, when having gaps in ordering. For example 3 RAM ports are used: 1, 5, 7. The ports 1 gets 50% RAM size allocation. The ports 5 and 7 get both 25% each. There is no advantage or disadvantage when allocating RAM indexes of the operators. Use either the automatic VisualApplets allocation or tune it manually, when a special design operator needs more RAM size than the other operators. |

The shared memory controller applies the Round & Robin algorithm and distributes the bandwidth evenly across all allocated ports. The algorithm is using the credits arbitration scheme: When a port gets active, it can stay active for the credit's clock cycles as long as the port provides new RAM jobs. Once a port is activated but has no more jobs, the port gets deactivated and the activation token jumps to the next port in line, which has request jobs pending. This way, the bandwidth is never wasted on idling. The credits are programmed by the firmware exclusively during synthesis of the applet depending on the amount of used RAM operators and can't be changed in the Framegrabber SDK/during runtime. The user has no access to the credit's programming. While an active port is owning the RAM interface, it will have access to 100% bandwidth of the memory controller. When all 8 ports are used and are active evenly, the resulting bandwidth over time is 1/8 for each port. In all other cases, the load on the ports defines the actual average bandwidth for each port.

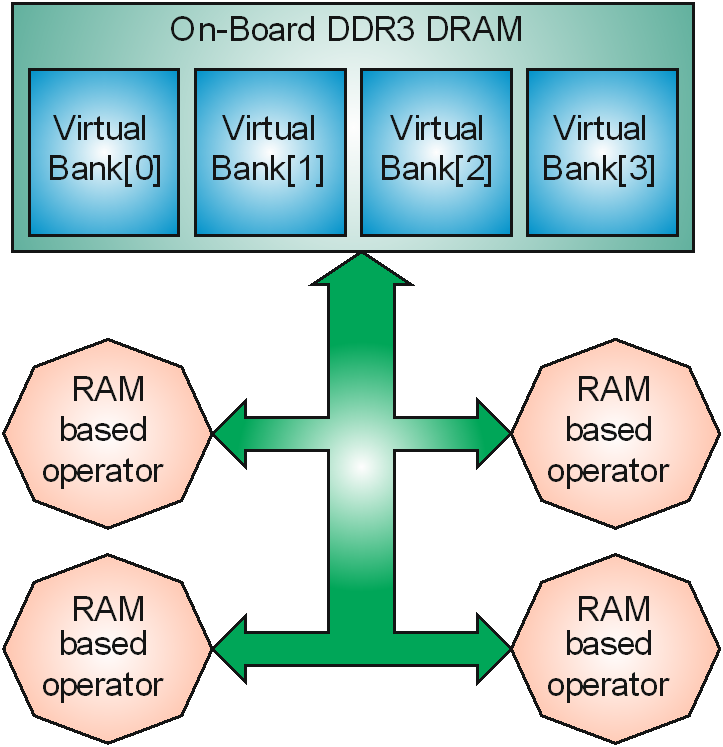

The platforms microEnable 5 marathon and LightBridge are assembled with only one physical RAM bank (the size of which is platform-specific). This single physical bank is formatted into 4 non-overlapping memory regions. These 4 regions are represented inside VisualApplets as 4 virtual RAM banks. When an operator reserves a RAM resource, it is using a virtual RAM bank which maps to an exclusive non-overlapping memory region inside the physical RAM.

The RAM bandwidth, however, is shared between all RAM based operators in a design. When a design utilizes all 4 RAM resources, each of the 4 RAM based operators can have up to 1.6 GB/s exclusive bandwidth, minus the efficiency factor of that particular operator. When only one RAM based operator is used in the design, this operator gets the total bandwidth of 6.4 GB/s. When 2 operators are used, each of the two operators gets half the total bandwidth, etc.

![[Note]](../common/images/admon/note.png) |

Bandwidth per Operator |

|---|---|

|

The on-board RAM provides 6.4GB/s total bandwidth. The bandwidth available for an individual RAM based operator is the total bandwidth divided by the number of all instantiated RAM based operators in the design. |

This RAM architecture needs to be considered when designing with RAM based operators.

Due to the shared bandwidth architecture, the applet developer should utilize all 256 bits of the operator’s memory interface (RAM Data Width) to achieve maximal throughput through the memory interface when using multiple RAM based operators even though the single RAM operator needs less bandwidth on its input.

Prev

Prev