Embedded VisualApplets allows you to use the graphical FPGA development environment VisualApplets for programming machine vision applications that will run on the FPGAs on your hardware platforms.

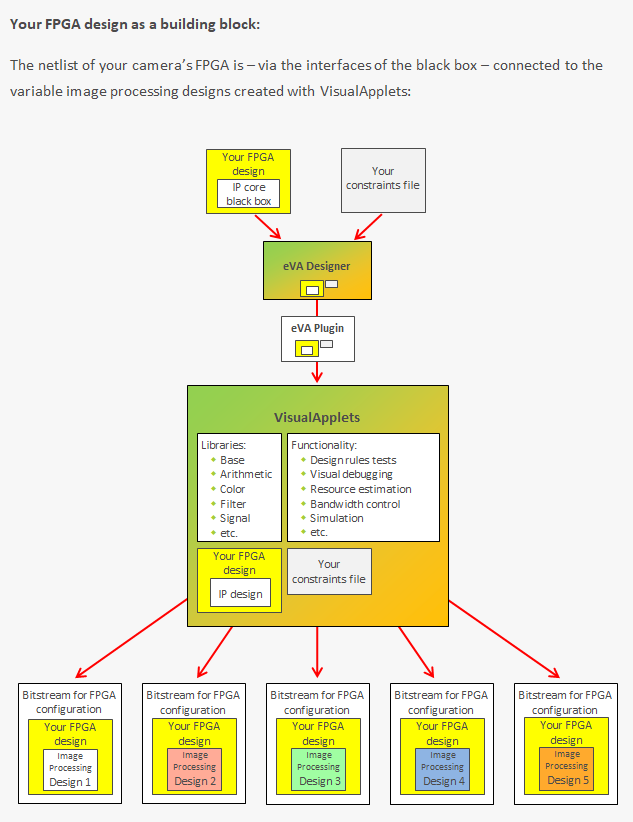

You do not program the whole FPGA with VisualApplets, but only an IP Core (Intellectual Property Core). This IP Core is embedded in your surrounding FPGA design:

To fill the IP core with logic for an image processing pipeline, no HDL knowledge is required, as VisualApplets is a graphical environment. VisualApplets also cares for the entire implementation flow. With VisualApplets, you enable software engineers and image processing experts to program the IP core on your hardware.

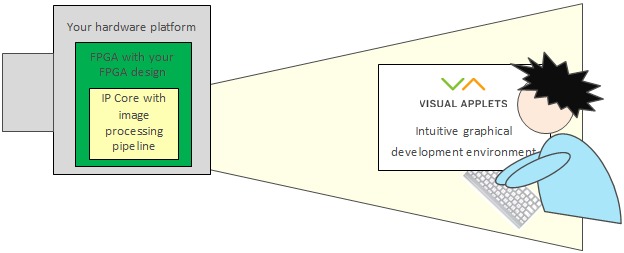

Before you can use VisualApplets to program applications for the FPGA on your hardware, you need to integrate the IP Core into your FPGA design and to generate an eVA (embedded VisualApplets) Plugin that provides VisualApplets with all hardware-specific details of your hardware platform.

You need to integrate the VisualApplets (VA) IP Core once. VA IP core: IP core in your FPGA that you can program with image processing functionality via VisualApplets. After integration, you can re-program the VA IP core as often as you want with as many machine vision applications as you want.

The key steps for hardware and software integration are carried out automatically by the tool eVA Designer (which comes as part of the VisualApplets Embedder package). This speeds up the work flow and leads to an implementation which is correct by construction.

You integrate VisualApplets into your hardware design in just a few steps:

-

You install VisualApplets.

-

You let eVA Designer generate an IP core black box in VHDL. The intuitive GUI supports you in specifying the details of the future VA IP core:

-

You enter some data regarding your hardware (hardware name, FPGA type, your vendor name etc.).

-

You specify the ports you want the VA IP core to have (image input ports, image output ports, register interfaces, memory interfaces, GPIs and GPOs).

-

You let eVA Designer generate the empty VA IP Core (VHDL black box) automatically, based on your inputs.

-

-

You integrate the generated IP core black box into your FPGA design (VHDL).

-

You generate a netlist of your FPGA design with integrated black box.

-

You create a constraints file.

-

You provide the netlist and the constraints file to eVA Designer and let it generate the hardware-platform-specific eVA Plugin Installer for VisualApplets.

-

You execute the eVA Plugin Installer. After installation, the hardware-platform-specific eVA Plugin is available in VisualApplets and allows to develop designs for the VA IP core on your FPGA.

After proceeding these steps, you can use the graphical development environment VisualApplets for programming the VA IP Core on your FPGA. A detailed step-by-step guide for these steps you find in 'Defining the IP Core Properties'.

Once-only implementation process for a new hardware platform:

By implementing the VA IP Core into your FPGA design, you enable software engineers and image processing experts to program the VA IP Core on your hardware.

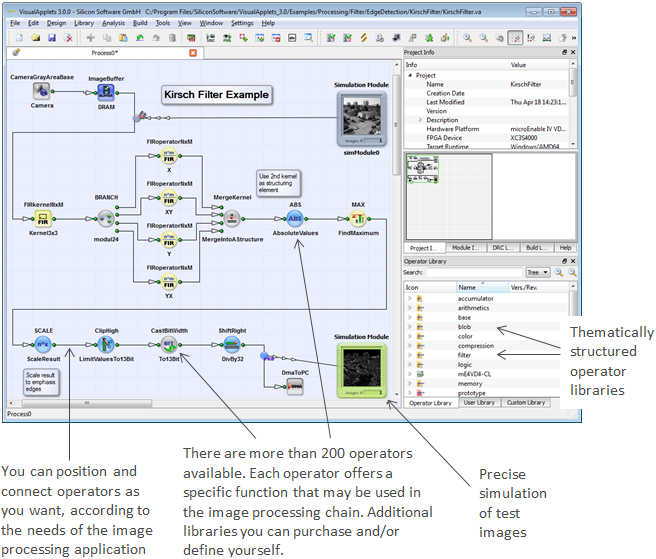

VisualApplets is used to design image processing programs (applets) for FPGA-based image processing. Designing applets with VisualApplets is easy. It is done in a graphical development environment. No knowledge of any hardware description language is necessary. In VisualApplets, an image processing solution is developed in form of a flow chart – without any HDL.

This is how a design looks like in VisualApplets:

Designs like in the figure above will later on (after synthesis into a bitstream) populate the VA IP Core on your hardware.

VisualApplets provides more than 200 operators. Each operator offers a specific function that may be used in the image processing chain.

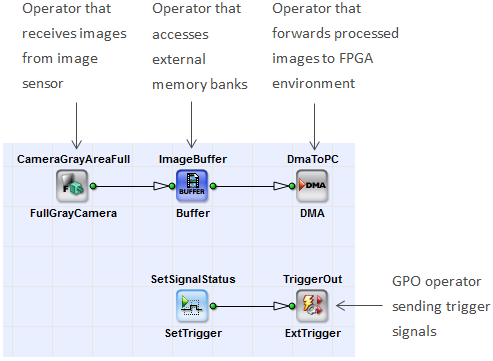

Some of the operators need to connect directly to the surrounding FPGA environment. These are:

-

Operators that receive images from the camera/sensor

-

Operators that deliver processed images at the end of the processing pipeline (e.g., operators delivering processed images to DMA)

-

Buffering operators using RAM resources

-

Operators allowing signal input and output (GPIOs)

For data communication between these operators and the surrounding FPGA design, the VA IP Core needs to provide according interfaces.

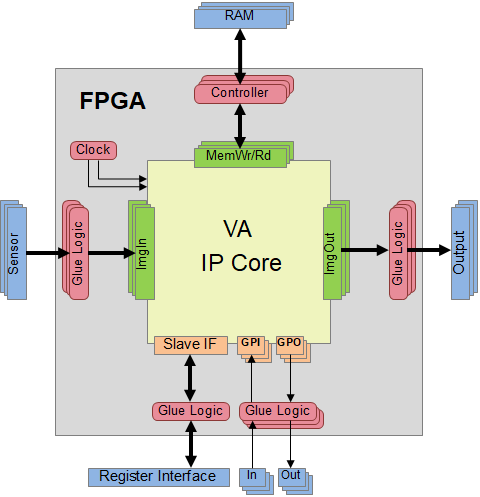

You can configure the interface ports of the VA IP core with a high grade of flexibility. The I/O of a VA IP core is composed of a number of flexible and easy-to-use interfaces between the IP core and your (surrounding) FPGA design. External hardware resources (like sensor interface, memory controller, etc.) are linked by glue logic in your FPGA design as shown in the figure below:

Interfaces that use a first-in-first-out buffer (FIFO) are marked green:

There are the following types of interfaces:

-

Clock: The IP core runs with two phase-synchronous design clocks where the second clock has twice the frequency of the first clock.

-

ImgIn: Interfaces for input streaming of image data Image data enters the IP core via a simple FIFO interface where additional flags for end-of-line and end-of-frame mark the frame boundaries. The number of ImgIn ports as well as the layout of data communicated via these ports can be configured.

-

ImgOut: Interfaces for output streaming of image data Image data leaves the IP core via a simple FIFO interface where additional flags for end-of-line and end-of-frame mark the frame boundaries. The number of ImgOut ports as well as the layout of data communicated via these ports can be configured.

-

MemWr/Rd: Interfaces for connecting external memory The IP core may be connected to external memory via an abstracted memory interface where any kind of memory can be connected via a single interface mechanism. External glue logic needs to adapt the IP core’s memory interface protocol to the used memory controller. The number of available memory interface ports can be configured. For each port, the interface properties may be defined individually (i.e., address and data width).

-

GPI, GPO : General purpose signal I/O Via GPI/GPO, signals may enter or leave the IP core. Such signals can be used for triggering and process control. The number of GPIO signals can be configured.

-

Slave IF: Register slave interface for runtime access to design parameters The slave interface is a simple register interface controlled by address, data, and control signals synchronous to the design clock. Controlling Reset and Enable of the implemented image processing pipeline(s) in the IP core is also done via the slave interface.

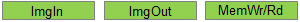

VisualApplets Embedder supports 12 performance classes. The individual performance classes are defined by the maximal sensor bandwidth, the FPGA resources that can be maximally used by the image processing application, and by the option to define memory interfaces:

You select the performance class. For pricing issues and licensing procedure, see section 'Licensing Model'. You need for a specific target hardware.

For entering data to the XML file (=hardware description file), you should use the GUI tool eVA Designer as described in section Defining the IP Core Properties. For each performance class, one XML template is available. You use the XML template to enter

-

the hardware specifics of your hardware platform,

-

a description of the interfaces you need at the VA IP Core,

-

the hardware-specific VisualApplets operators that connect to the interfaces from within the VA IP core.

![[Note]](../common/images/admon/note.png) |

Available Templates |

|---|---|

|

Your VisualApplets installation comes with two example platform descriptions (XML), as well as with one template that allows you to enter the details of your own hardware from scratch. These XML files are for testing purposes. They allow the generation of restricted eVA Plugins. Applets created with these plugins are runtime-limited. The XML example platform descriptions and template you find in your runtime installation, folders:

With your own, vendor-specific XML templates for each performance class you will be provided directly by Basler. |

To integrate the VA IP Core into your FPGA design and to generate an eVA plugin that provides VisualApplets with all hardware-specific details of your hardware platform, you need the following components:

Hardware & Operating System:

-

PC running operating systems Microsoft Windows 7, Windows 8, or Windows 10 (64bit)

-

PC Memory: Minimum 4 GByte, recommended: 8 GByte or better

-

Minimum available hard disk space: 500 MByte

-

Target hardware platform with implemented FPGA. At the point of release of VisualApplets 3.2, FPGAs of Xilinx Inc. starting from series 6 are supported (including Zynq7000, Series 7 FPGAs, Ultrascale, Ultrascale+, and Zynq Ultrascale+).

Software:

-

VisualApplets 3.0 (or higher)

-

VisualApplets 3 license

-

VisualApplets 3 Embedder license

-

XML template for creating a hardware description (delivered by Basler)

Third-Party-Software for synthesizing image processing applications:

-

For compiling the SDK examples, a C++ Compiler is necessary.

-

For generating the actual bitstream out of your design, you need a tool suite provided by the FPGA manufacturer. The tool flow is completely controlled by VisualApplets. You simply need to install it. Depending on the FPGA type you have implemented, you need (at point of release of VisualApplets 3.0) either

-

Xilinx Vivado (feeless WebPACK edition or Design Suite), or

-

Xilinx ISE (feeless WebPACK edition or Design Suite).

For details, please refer to the documentation of the FPGA type you have implemented on your hardware.

-

Prev

Prev