VisualApplets allows you to export VisualApplets designs as Tcl script (*.tcl).

You can use the script format for the following purposes:

-

revision control

-

comparing versions automatically (by creating "diffs")

However, some information is lost during export to Tcl script.

Therefore, you should always save your design in *.va format.

The Tcl file is not qualified to be used as the primary data format.

![[Warning]](../common/images/admon/warning.png) |

Save Design in *.va Format

|

|---|---|

|

Use the The Tcl script does not contain the full design information. |

The following information is lost during export to Tcl script:

-

The local modifications you made in a user library element instance (to adapt the instance to the surrounding design) are lost. If you re-import a Tcl script into VisualApplets, the instance is inserted as a fresh copy of the user library element. The content of the instance in your design has not been saved in Tcl.

-

The content of info boxes is kept in Tcl format. However, the formatting of info boxes is lost.

You should always save your design in *.va format, too.

The Tcl file is not qualified to be used as the primary data format.

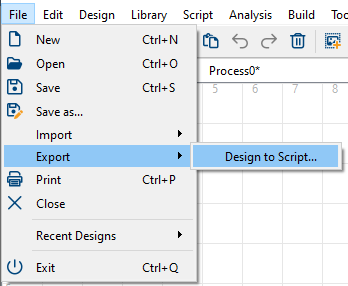

To export your design to a Tcl file (*.tcl):

-

From the menu, select → → .

-

Select a location for the

*.tclfile containing your design, and click on Save.

Now you can check in the Tcl file into your version control system, or find differences between different versions of the design using a "diff" tool.

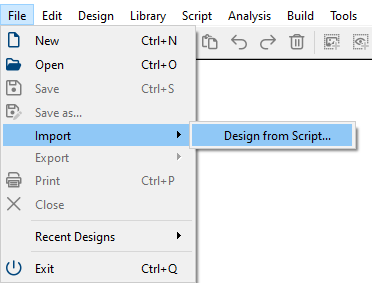

To import your *.tcl design file into VisualApplets:

-

From the menu, select → → .

-

Browse to the location of the

*.tclfile containing your design, and select the *.tcl file. -

Click on Open.

Now your design is opened in VisualApplets, and you can

-

continue editing your design within VisualApplets,

-

save your design file as

*.vafile.

![[Warning]](../common/images/admon/warning.png) |

Always use *.va File Format as Primary Data Format

|

|---|---|

|

Always use the Never use the Tcl script format as primary data format, as the Tcl script does not contain the full design information. |

In the generated Tcl source file the following VisualApplets-specific commands are used.

![[Important]](../common/images/admon/important.png) |

Syntax |

|---|---|

|

Optional parameters: The notation of optional parameters follows the Wirth Syntax Notation (brackets). Parameter FullModuleName: Hierarchical path starting at process level. The hierarchies are separated by a slash. |

|

Command |

Parameters |

Description |

|---|---|---|

|

Creating, Loading, and Saving Designs |

||

|

CreateDesign |

Name Platform |

Command for creating a new design with the name "Name" for a hardware platform "Platform". For specifying the target platform of the design, you can either use

Using capitals in the names has no effect. |

|

SetDesignProperty |

Key Value |

Use this command to enter design properties. There are tree values you can use as key:

|

|

SetDesignClock |

NewFrequency |

Command for setting the basic clock frequency of the FPGA (in MHz). |

|

Setting up a Design |

||

|

CreateProcess |

- |

Creates a new process |

|

CreateModule |

OperatorType FullModuleName [ InPortMultiplicity [ OutPortMultiplicity {NamedPortMultiplicity} ] ] xPos yPos |

Creates an instance (Module) of an operator (OperatorType). The position of the module in the design window you define via parameters xPos and yPos. With FullModuleName you define the module's hierarchical position within the design and it's name after instantiation (e.g., Process0/branch). Optionally, you can use the value pair InPortMultiplicity and OutPortMultiplicity to specify the multiplicity of the vector inputs and vector outputs of the module. If you use this value pair, you define the number of ports (in operators with variable port numbers, like BRANCH) for the module (which is a specific instance of an operator). In addition, you can specify the multiplicity of individual vector ports (NamedPortMultiplicity). You can use NamedPortMultiplicity multiple times in one command line. The format is PortGroup:Number. Example: CreateModule BRANCH Process0/branch 0 0 O:3 100 100 |

|

ConnectModules |

FromModule FromModulePort ToModule ToModulePort [ x1 [y2 x3] ] |

Command for connecting modules. For FromModule and ToModule, use hierarchical names (names containing the hierarchical position of a module within a design plus actual module name, e.g., (e.g., Process0/branch). Nodes within hierarchical boxes are identified via the prefix "INBOUND#" or "OUTBOUND#". Example: "OUTBOUND#O001". The optional parameters x1, y2 and x3 you use to define the geometry of the connecting polygon (horizontal line from FromModuleOutputPort to x1, vertical line to y2, horizontal line to x3, vertical line up to the height of ToModulePort, horizontal line to ToModulePort). |

|

CreateComment |

FullModuleName Text xPos yPos |

The content of Text can contain Unicode characters. If you use characters that are not part of ASCII, use the according Tcl syntax to represent Unicode, for example: [encoding convert from utf-8 "A-Umlaut: \xc3\x84"] |

|

SetParamInt |

FullModuleName ParameterName Value |

Command for setting an integer parameter. |

|

SetParamFloat |

FullModuleName ParameterName Value |

Command for setting a floating point parameter. |

|

SetParamEnum |

FullModuleName ParameterName Value |

Command for setting an addressed enum parameter. Value is the string of the enum value. Example: Process0/module1 (SetSignalStatus), "SetParamEnum Process0/module1 Mode High" sets parameter Mode to High. |

|

SetParamString |

FullModuleName ParameterName Value |

Command for setting a string parameter. |

|

SetParamIntField |

FullModuleName ParameterName Index Value1 {OtherValues} |

Command for setting integer field entries starting with index "Index" for the following values. |

|

SetParamFloatField |

FullModuleName ParameterName Index Value {OtherValues} |

Command for setting float field entries starting with index "Index" for the following values. |

|

SetParamStatic |

FullModuleName ParameterName |

If a parameter can be static as well as dynamic, in the vast majority of cases the parameter is set to dynamic per default. Use this command to set such a parameter to static. |

|

SetParamDynamic |

FullModuleName ParameterName |

You can use this function to set a parameter to dynamic (if the parameter can be can be dynamic at all). |

|

SetLinkParam |

FullModuleName PortName ParameterName Value { OtherParameterName OtherParameterValue } |

Command for configuring links. The connection is identified via the connection node of a module. |

|

SetResourceMapping |

FullModuleName ResourceName [Index] NewMapping |

Command for changing the mapping of resources to a module. The resource ResourceName will be mapped to the new index NewMapping. In case the module allocates multiple resources of the same type, use the optional parameter Index for selecting the resource. |

|

Further Editing Commands |

||

|

Move |

FullModuleName [HierNodeName] PosX PosY |

Command for re-positioning a module, a H-Box node, a comment box, or a simulation module to a new position within the design window. Use parameter [HierNodeName] only for selecting an H-Box node. Nodes within hierarchical boxes are identified via the prefix "INBOUND#" or "OUTBOUND#"(like you do when using command ConnectModules), for example, "INBOUND#I000". |

|

CreateSimSource |

FullSimModuleName xPos yPos |

Command for creating a simulation source on the indicated position. |

|

CreateSimProbe |

FullSimModuleName xPos yPos |

Command for creating a simulation probe on the indicated position. |

|

ConnectSimModule |

FullSimModuleName TargetModuleName TargetModulePortName [ xPos yPos ] |

Command for connecting a simulation module with a link. The connection is identified via the specified module (TargetModuleName) and port (TargetModulePortName). TargetModuleName must be located in the same hierarchy as FullSimModuleName. Optionally, you can define the position of the connection on the link via the parameters xPos and yPos. |

|

SetSimModuleProperty |

FullSimModuleName Key Value {OtherValue} |

Command for configuring a simulation module. The following parameters can be set (in the list below, the key word Key is followed by the parameter values Value): PixelAligmentOffset BITS ImageFileSubPixels NUMBER ImageFilePixelBits BITS ImageFileNormalize CHOICE where CHOICE = "1" | "0" | "yes" | "no" | "on" | "off" | "true" | "false" CropRect [imageNr] X Y WIDTH HEIGHT CurrentImage INDEX |

|

AddImage |

FullSimSourceName ImageFileName1 {OtherImageFileName} [ImageLibrary] |

Command for adding an image to a simulation source. If the number of kernel elements on the link is > 1, you need to specify as many images as there are kernel elements on the link. Optionally, you can specify the image library you want to be used ( ImageLibrary = "Native" | "ImageMagick"). |

|

User Libraries |

||

|

InstUserLibOperator |

LibName OperatorName FullModuleName XPos YPos |

Command for instantiating a user library element. |

|

Custom Library Handling |

||

|

InstCustomLibOperator |

LibName OperatorName FullModuleName XPos YPos |

Command for instantiating a custom library element. |

Table 13. Commands for Creating and Editing a VA Design in Tcl

Prev

Prev